Automation

(Last updated: Wednesday, November 20,2019)

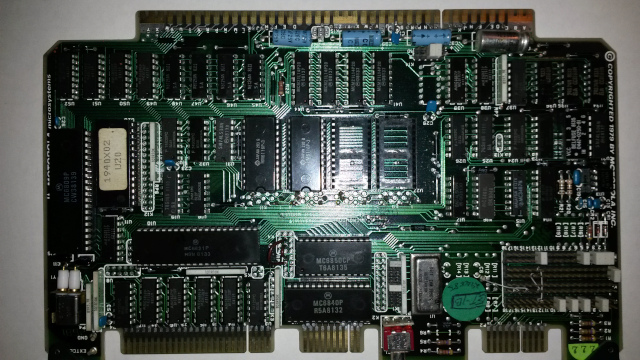

Motorola M68MM19A 68B09

This is a Motorola M68MM19A 68B09 Single Board Computer. This is an Exorciser board and a Motorola Design from 1979. So far I have a little information on the board but I'm pretty sure I can easily reverse engineer the board as it appears to be based on a Motorola reference design.

Discovered that this one has no ROM on it. They can go in the U27 - U30 locations but so can static RAM. I'll need to figure that out later. What I thought was a ROM (U20) is actually an 82100 (FPLA).

- 68B09 - The Motorola 6809 CPU, B speed rating.

- 68B50 - ACIA (Asynchronous Communication Interface Adapter)

- 68B40 - PIT (Programable Interface Timer)

- 68B21 - PIA (Parallel Interface Adapter)

- 27xx - EPROM (2716/2732) U27 - U30

- 82S100 - PLA U20 (address CE logic)

- 6116 - U29 & U30, 2KB (2K x 8) Static ram

- M8T26A - Quad Tri-state bus transceiver

- 2114 - x4, 1K x 4 bit This is a strange selection. I need to figure out where this on the memory map.

(Alas, the MM19A doesn't have DAT...) I'm curious about the use of the 2114 (1Kx4) chips, some of the other boards from that era also use the 2xxx chips. These differ from the 'normally' used 6116 (2K x 8). At least the 61xx Static RAMs were the more common when I got started in 1982. I know the 74189 (64 x 4) is often used for DAT (an SWTPC design but also found on GIMIX 6809 CPU boards). I've seen a recent design where a 6116 was used and I've found documentation where CMS designed a board that used the full 6116 for DAT plus other information for up to 128 processes (OS9 supported this). While all these 'tricks' such as DAT seem quaint by modern standards they were revolutionary for the time. One of the CMS boards had DAT (2K vs the SWTPC 64 bytes) and extra logic that would push extra instructions to the CPU to speed up interrupts. This was a crude form of interrupt vectoring. Back then every cycle counted when you had all that task switching.

Dave Wiens found this information on the Motorola Micro Modules (ie MM19A):

Memmap -

0000 - BFFF - Available

C000 - C7FF - U27 - 2K (note 4)

C800 - CFFF - U28 - 2K "

D000 - D7FF - U29 - 2K "

D800 - DFFF - U30 - 2K "

E000 - E7FF - 2114x4 - 2K (Not DAT)

E800 - EFFF - PTM/ACIA/PIA (need further info)

F000 - F7FF - U27 - 2-4K (note 4 & 5)

F800 - F8FF - U28 - 2K (note 4 - if U27 is not 4K)

Notes:

4: U27 & U28 move from F000 to C000 when used with DEBUG board

5: U27 moved from F000 to A000 when used with DEBUG board

6: Address map may be reprogrammed as follows: MM19 - 82S100 FPLA

Mike Naberezny's PLA Replacement for the Commodore 64

Please note: I've taken some liberty with copying parts of Mike's page here. I didn't steal the idea but found this useful so I'm giving credit where due. I actually recall this from previous dicussions with other engineers when this was done in the 1970's with much smaller proms. Also this may not work with the MM19A (or other devices that use the 82S100).

PLA Replacement

Many Commodore 8-bit computers implement the Signetics 82S100 FPLA, commonly known as a “PLA” chip by owners. This is a one-time programmable logic device that was programmed by Commodore. This part is one of the most common failures for all computers that use it.

Unfortunately, the 82S100 has not been produced in quite some time and finding a device programmer that supports it is also difficult. Without a drop-in replacement available, users began seeking an alternative. Some have reconstructed the logic equations and building replacements using more modern programmable logic parts. Others have attempted to replace the PLA with an EPROM. Both methods have had varied success.

EPROMs are available with much faster access times than were available when the Commodore computers were produced. It is now possible to obtain 45ns EPROMs with timing characteristics similar to 82S100. In June 2008, I purchased some AM27C512-45 parts and began experimenting with them as a replacement for the 82S100. I was able to successfully repair my CBM 8296D using this method and have since used the technique on several other models.

Adapter

The 82S100 and 27C512 have similar pinouts but are not compatible. Several pin swaps must be made before a 27C512 can be installed in a socket intended for an 82S100. This could be done by producing a small daughterboard or by hand-wiring.

To save the cost, I came up with a simple technique of modifying a standard 28-pin DIP socket. The 27C512 is installed on this socket, which is then installed into the computer’s socket intended for the 82S100.

The first step is to solder four wires onto the socket. I used 30 AWG Kynar wire, the same type of wire that is typically used for wirewrapping. Four pins on the EPROM are then bent out slightly and the EPROM is installed on the socket. Finally, the wires are tacked to the EPROM.

Need to come up with the PROM contents and the schematic for a drop in ROM and board.

82S100 Pin out (for the Commodore 64)

The 82S100 is a Tri-stat FPLA of 16x48x8 (16 inputs, 48 terms, 8 outputs).

| Pin | Name | Remarks |

|---|---|---|

| 1 | FE/NC | Used for programming field-programmable parts and not connected internally for mask programmable parts. |

| 2 | I7 | Connected to A13 of the address bus (input 7) |

| 3 | I6 | Connected to A14 of the address bus |

| 4 | I5 | Connected to A15 of the address bus |

| 5 | I4 | Connected to #VA14 on VIC-II |

| 6 | I3 | Connected to #CHAREN on I/O port of the 6510 CPU |

| 7 | I2 | Connected to #HIRAM on I/O port of the 6510 CPU |

| 8 | I1 | Connected to #LORAM on I/O port of the 6510 CPU |

| 9 | I0 | Connected to #CAS on the VIC-II |

| 10 | F7 | #ROMH (output 7) |

| 11 | F6 | #ROML (output 6) |

| 12 | F5 | #I/O |

| 13 | F4 | GR/#W, connected to #WE on the color RAM |

| 14 | VSS | GND |

| 15 | F3 | Connected to #CS1 on the #CHARROM |

| 16 | F2 | Connected to #CS on the #KERNAL ROM |

| 17 | F1 | Connected to #CS on the #BASIC ROM |

| 18 | F0 | #CASRAM, connected to the #CAS pin on the DRAM |

| 19 | #CE | Chip Enable |

| 20 | I15 | Connected to VA12 on VIC-II |

| 21 | I14 | Connected to VA13 on VIC-II |

| 22 | I13 | Connected to #GAME on pin 8 of cartridge port |

| 23 | I12 | Connected #EXROM on pin 9 of cartridge port |

| 24 | I11 | Connected to R/#W of the bus |

| 25 | I10 | #AEC, connected to inverted version of AEC on the VIC-II |

| 26 | I9 | Connected to BA on the VIC-II |

| 27 | I8 | Connected to A12 of the address bus |

| 28 | VCC | +5V |

Notes:

Links

- Motorola Micromodules Overview - 1980 (pdf)

- PLA Replacement

- PLA Replacement (Git hub)

- SWTPC S/09 Dynamic Address Translation

- GITHUB CMS_SBC - Disassembly of 6809 based CMS 9609, 9619, 9639 and 9642 SBC Monitor ROMs

- Crapple - CMS SBC